## Bringing up the OpenHW Group RISC-V tool chains

Jeremy Bennett

Copyright © 2023 Embecosm &OpenHW Group. Freely available under a Creative Commons Attribution-ShareAlike license.

#### About Open Hardware Group

- Not-for-profit member driven RISC-V collaboration

- global: industry, academic and individuals

- Goal is high quality, open source hardware development

- collaborative and open development model

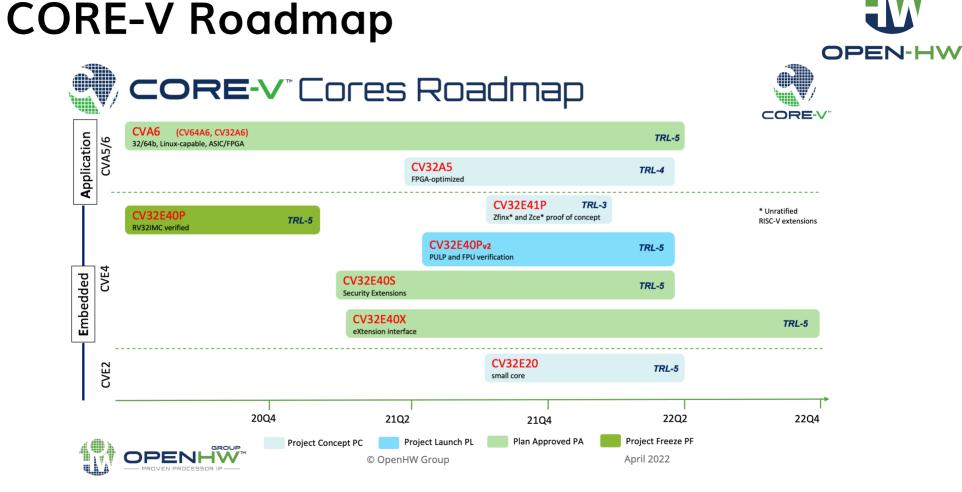

- Cores are developed as the <u>CORE-V</u> family

- smallest RV32 to largest RV64 designs

- standard RISC-V with custom ISA extensions

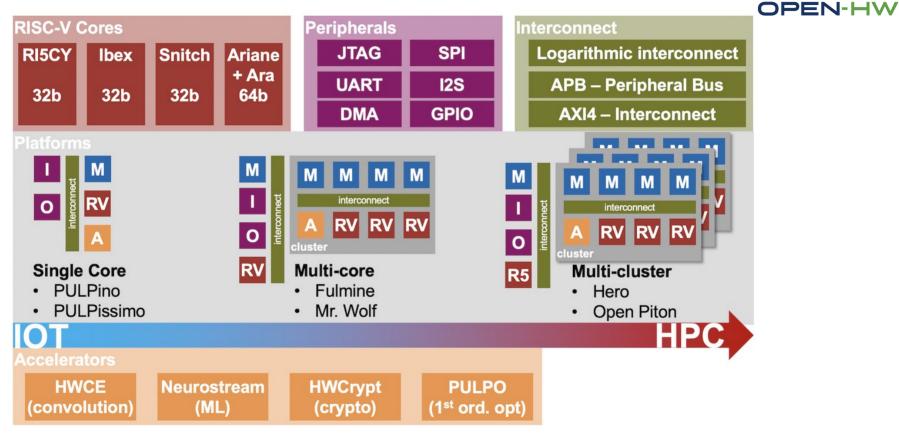

## **Open Hardware Group Ancestry: PULP**

#### **Open Hardware Group Members**

Partners

XLINX

WMM

cådence

Image: Comment of the second of t

# **OpenHW Engineering Organization**

- <u>Technical Working Group</u> (TWG): Jérôme Quevremont, David Lynch

- top level oversight

- Cores TG: Arjan Bink, Jérôme Quevremont

- oversees development of cores

- Verification TG: Simon Davidmann, Jean-Roch Coulon

- oversees verification of cores

- Hardware TG: Hugh Pollitt-Smith, Tim Saxe

- responsible for reference SoC implementations

- Software TG: Jeremy Bennett, Yunhai Shang

- responsible for all software projects

#### Software TG Projects

- Discussed today

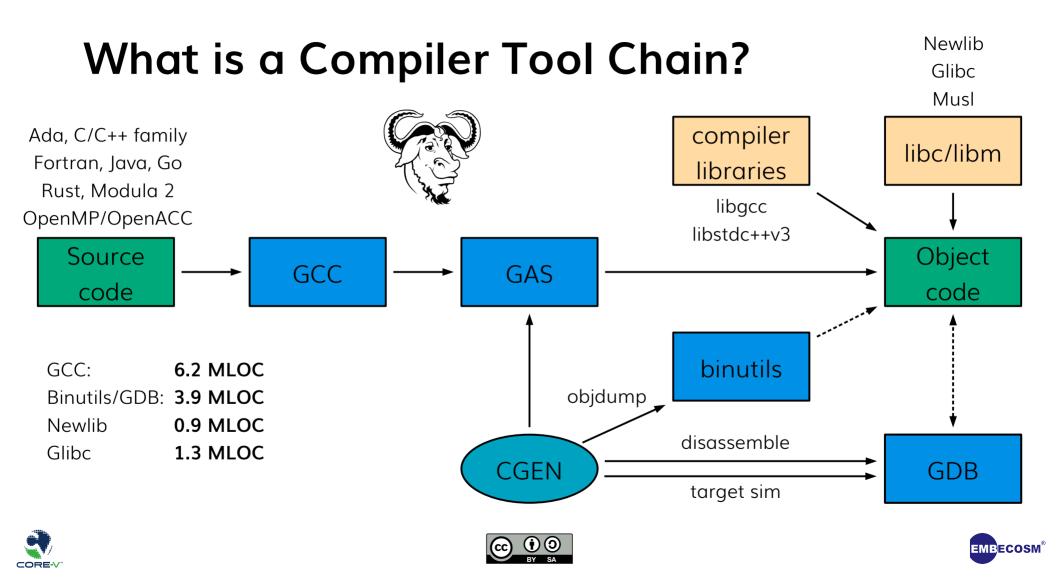

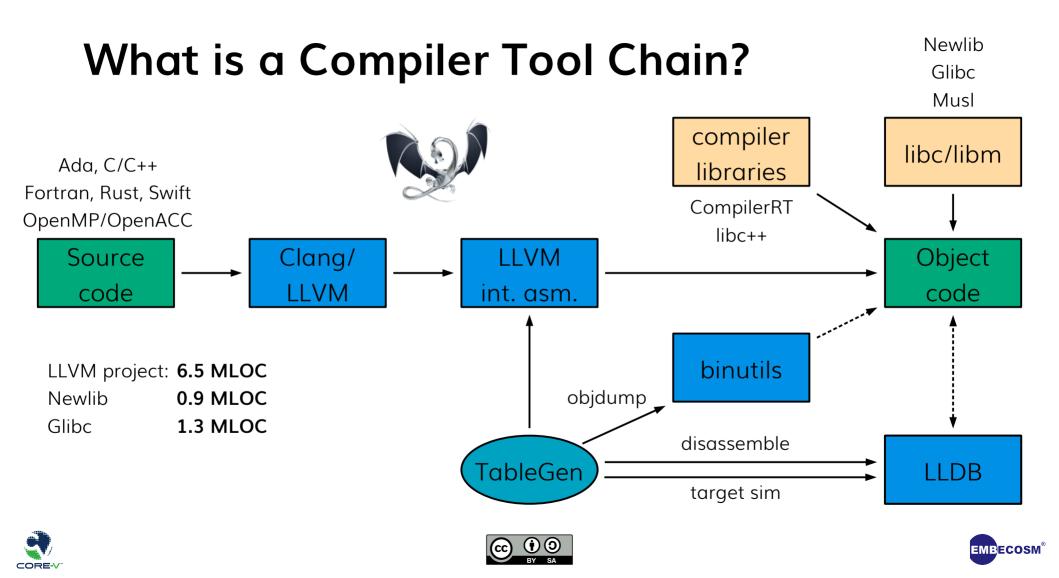

- LLVM project

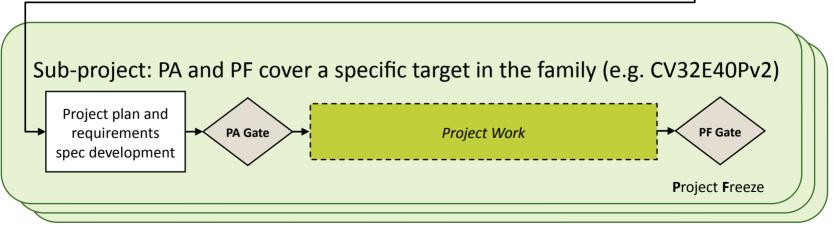

- GNU tools

- QEMU

- Verilator model

- Other

- SDK

- Hardware abstraction layer

- FreeRTOS

- Linux

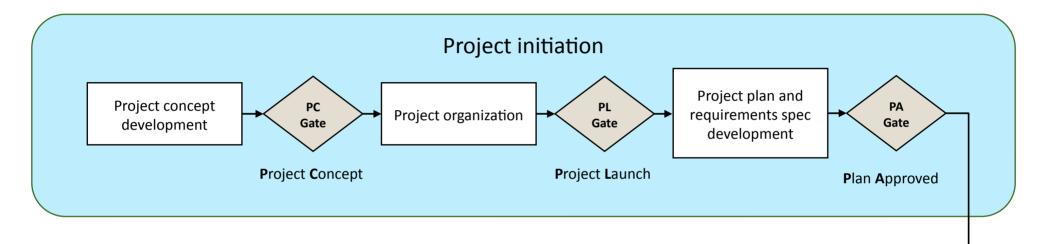

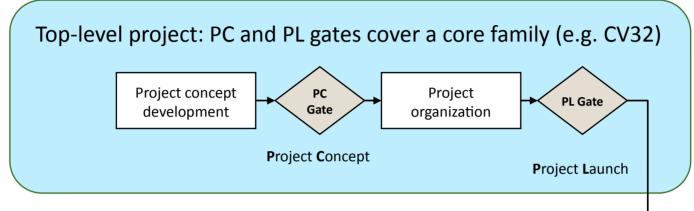

#### **OpenHW Process Gates**

#### **OpenHW Process Gates (SW)**

#### **CORE-V ISA Extensions**

- Post-incrementing load/store (25): -march=rv32i\*\_xmem

- Hardware loops (6): -march=rv32i\*\_xhwlp

- General ALU operations (31): -march=rv32i\*\_xalu

- Immediate branching operations (2): -march=rv32i\*\_xbi

- Multiply-accumulate (22): -march=rv32i\*\_xmac

- Event Load (1): -march=rv32i\*\_xelw

- PULP Bit manipulation (16): -march=rv32i\*\_xbitmanip

- PULP SIMD (220): -march=rv32i\*\_xsimd

- Zc\* 0.7.5 (36): -march=rv32i\*\_zc\*

**PUIP**

extensions

#### **CORE-V Builtin Functions**

- Total around 300 functions defined

- Naming convention

- \_\_builtin\_riscv\_cv\_isaext\_name

- except where map to standard names (e.g. \_\_builtin\_abs)

- Support 32-bit and 64-bit versions with same name

- Not always 1:1 mapping to assembler instructions

- See core-v-sw/specifications/corev-builtin-spec.md on GitHub

- 57 pages!

#### Testing

- Need a target with all the ISA extensions supported

- compile time testing can be done without

- QEMU for CORE-V

- project led by Weiwei Li at PLCT, Beijing

- work in progress, due later in 2023

- Verilator model of specific cores

- needs a debug server interface

- for CV32E40Pv2 work in progress, due Q1/2023

#### **Testing Policy**

- LLVM project uses *lit* and GNU regression test (subset)

- GNU tools project uses GNU regression tests

- Exhaustive positive and negative testing by gas

- Vendor specific GNU ld testing

- Compilation only tests of builtins

- scan for assembler instructions

- Execution tests of inline assembler and builtins

#### **Key Issues**

- Resourcing

- thanks to Embecosm, PLCT, Silicon Labs and Dolphin Design

- but needs more

- Upstreaming as vendor specific versions

- OpenHW Group will not maintain forks long term

- riscv32-corev-elf-gcc, risv32-corev-elf-clang etc.

- need PSABI SIG to agree vendor specific relocations

- ISA extension versioning (especially in gas)

#### **Get Involved**

- Repositories (all in GitHub openhwgroup org)

- corev-llvm-project

- corev-binutils-gdb

- corev-gcc

- embdebug-target-core-v

#### **Get Involved**

- Project leads

- LLVM project: Charlie Keaney (overall) and Chunyu Liao (CV32E40Pv2)

- GNU tools: Nandni Jamnadas

- QEMU: Weiwei Li

- Verilator model and debug server: Jeremy Bennett

- Weekly 30 minute engineering meetings

- LLVM project: 08:30 UTC every Friday

- GNU tools: 09:00 UTC every Friday

#### **Thank You**

#### jeremy.bennett@embecosm.com

embecosm.com www.openhwgroup.org Jeremy Bennett

Copyright © 2023 Embecosm &OpenHW Group. Freely available under a Creative Commons Attribution-ShareAlike license.